注意!このドラフト仕様は、RISC-V Foundationに標準仕様として承認される前に変更される可能性があります。

本章では、RISC-Vのハイパーバイザ拡張について説明する。ハイパーバイザ拡張は、Type-1、Type-2ハイパーバイザ上にゲストのオペレーティングシステムの効率的なホスティングをサポートするためのスーパバイザレベルアーキテクチャを仮想化するためのものである。ハイパーバイザー拡張は、スーパーバイザーモードをハイパーバイザー拡張スーパーバイザーモード(hypervisor-extended supervisor mode : HSモード もしくは単純にハイパーバイザーモード)に変更する。このモードはハイパーバイザーもしくはホスティング可能なオペレーティングシステムが動作するためのモードである。ハイパーバイザー拡張はもう一別のアドレス変換モードを追加する、これはゲスト物理アドレス (Guest Physical Address)からスーパーバイザー物理アドレス(supervisor physical address)に変換するものであり、これによりゲストオペレーティングシステムのメモリおよびメモリマップドなI/Oサブシステムを仮想化する。HSモードはSモードと同様に動作するが、Sモード以外の命令とCSRレジスタが使用可能であり、これによりアドレス変換の新しいステージを制御しゲストOSを仮想的なSモード(VSモード)で動作することをサポートする。通常のSモードのオペレーティングシステムはHSモードとVSモードのゲストを変更することなく動作することができる。

HSモードでは、OSもしくはハイパーバイザは、OSが通常通りSモードで動作しているのと同様なSBIを使ってマシンとやり取りを行う。HSモードのハイパーバイザーは、VSモードのゲストのためにSBIを実装することが期待されている。

ハイパーバイザー拡張は、misaCSRの7ビット目、つまりアルファベットのHに相当するビットを設定することによって有効化される。ハイパーバイザーを実装したRISC-VのHARTはmisa[7]をハードワイヤにすることは推奨されておらず、この拡張を無効化することも可能にしておくべきである。

ベースラインの特権アーキテクチャは、ゲストOSがユーザーレベルで実行される従来の仮想化技術の使用を簡素化するように設計されている。これは、いくつかの特権命令を簡単に検出してトラップできるためである。 ハイパーバイザー拡張機能は、これらのトラップの頻度を減らすことにより、仮想化のパフォーマンスを向上させる。 ハイパーバイザー拡張機能は、ハイパーバイザーをSモードで実行し、ハイパーバイザーCSRアクセスのためにMモードにトラップし、シャドウページテーブルを維持することにより、拡張機能を実装しないプラットフォームで効率的にエミュレートできるように設計されている。 Type-2ハイパーバイザーのCSRアクセスの大部分は、有効なSモードアクセスであるため、トラップする必要はない。 ハイパーバイザーは、ネストされた仮想化を同様にサポートできる。

5.1 特権モード¶

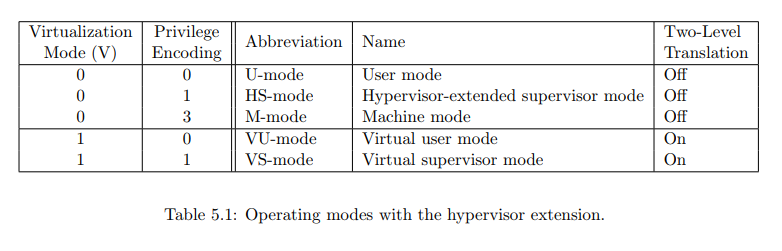

“V”で表現される現在の仮想化モード(virtualization mode)はHARTがゲスト上で実行しているかどうかを示すものである。V=1であれば、HARTは仮想的なSモード(VSモード)もしくはVSモードで動作しているオペレーティングシステム上で仮想的なUモード(VUモード)として動作していることを意味する。V=0であれば、HARTはMモード、HSモード、もしくはHSモードで動作しているOS上のUモードで動作している。仮想化モードは、同様に2ステージアドレス変換モードが有効(V=1)か無効(V=0)であるかも示している。表5.1はRISC-V HARTのハイパーバイザー拡張における動作モードの一覧である。

1540735375336¶

メモ:

仮想モード(Virtualization Mode, Vビット)により、現在のHartがゲストとして実行されているのかどうかを判定する。

V=1 : 仮想Sモード(VSモード), 仮想Uモード(VUモード)で動作している。これはゲストOS上で動作していることを意味する。また、V=1の場合は2レベルアドレス変換が有効である。

V=0 : Mモード, HSモード, HSモード下のOS上で動作しているUモードのどれかである。

5.2 ハイパーバイザCSR¶

HSモード上で動作するOSとハイパーバイザは、例外と割り込み、アドレス変換を処理するためにスーパバイザCSRを使用する。追加のCSRはHSモードモード上で実装されており、VSモードで実装されていない。しかし、VSモードの2レベルアドレス変換と動作の制御を管理するために使用である。これらは、

hstatus, hedeleg, hideleg, hvip, hip, hie, hgeip, hgeie, hcounteren, htimedelta, htimedeltah, htval, htinst, hgatpである。

さらに、いくつかの仮想スーパーバイザーCSR (VS

CSR)は通常のスーパーバイザーのレプリカである。例えば、VS

CSRであるvsstatusは通常のsstatusCSRのコピーである。

V=1のとき、VS CSRは該当するスーパーバイザーCSRの代替となる。特に指定されない限り通常のスーパーバイザーCSRの機能をすべて受け継ぐ。スーパーバイザーCSRに対する通常の読み書きの命令は、すべてVS CSRへのアクセスに置き換えられる。V=1のとき、別々のCSRアドレスに定義されたVS CSRに直接読み書きを行おうとするとそれは仮想命令例外が発生する。(Uモードで当該動作を実行しようとすると、通常の無効命令例外が発生する。)VS CSR自体は、MモードもしくはHSモードでのみアクセス可能である。

V=1の時、通常のHSレベルのスーパーバイザーCSRはVS CSR置き換えられる。この時スーパーバイザーCSRの値は保持されるが、特に文書化されない限り直接マシンの動作に影響を与えない。逆にV=0である場合、VS CSRは読み書き可能であるものの、マシンの動作に直接影響を与えない。

いくつかの標準的なスーパーバイザーCSR(scounterenや、N拡張が実装されている場合のsedelegおよびsideleg)には、VS

CSRに該当するCSRが用意されていない。これらのスーパバイザ―CSRは、V=1であっても、VSモードおよびVUモードがHSモードおよびUモードに置き換えられることを除いて引き続き通常の機能とアクセシビリティを保持している。ハイパーバイザーのソフトウェアは必要に応じてこれらのレジスタの内容を手動でスワップすることを期待されている。

一致するVS CSRは、複製する必要があるスーパーバイザCSRにのみ存在している。これは主に、トラップによって自動的に書き込まれるもの、またはトラップエントリの直後やSRETの直前で、ソフトウェアだけではまさに適切な瞬間にCSRをスワップできない場合に命令の実行に影響を与えるものである。 現在、ほとんどのスーパーバイザーCSRはこのカテゴリーに分類されるが、将来のCSRは分類されない可能性がある。

本章では、HSモードでの有効なXLENのことをHSXLENと呼び、VSモードでの有効なXLENのことをVSXLENと呼ぶ。

メモ:

V=0

バックグラウンドCSR : VSモードの情報

フォアグラウンドCSR : HSモードの情報

V=1

バックグラウンドCSR : HSモードの情報

フォアグラウンドCSR : VSモードの情報

HSモード時のXLENのことをHSXLENと呼ぶ。

5.2.1 ハイパーバイザーステータスレジスタ (hstatus)¶

hstatusレジスタはHSXLENビットの読み書き可能なレジスタである。HSXLEN=32の場合のフォーマットを図5.1に、HSXLEN=64の場合のフォーマットを図5.2に示している。hstatusレジスタはmstatusと同様の機能を提供するレジスタであり、VSモードのゲストの例外動作の制御及び記録を行っている。

図5.1: RV32時のハイパーバイザーステータスレジスタhstatus¶

VSXLフィールドはVSモード時の有効なXLEN値(この値がVSXLENとなる)を制御している。VSXLEN値はHSモード時のXLEN値(HSXLEN)と異なっていても良い。HSXLEN=32の時、VSXLフィールドは存在せず、VSXLEN=32となる。HSXLEN=64のとき、VSXLフィールドはWARLフィールドとなり、ページ16の表3.1のmisaレジスタのMXL値と同様にエンコードされる。特殊なケースとして、VSXLEN=HSXLENであることが常に保証されるような実装の場合には、VSXLフィールドはRead-Onlyとして実装されることが許されている。

HSXLENの値が32からより大きな値に変更され、かつVSXL値が複数の値を許可する場合、VSXLの値は新しいHSXLEN値よりも小さく、かつ該当するサポート可能な最大値へと変更される。

hstatusのフィールドVTSR, VTW, VTVMはmstatusのTSR, TW,

TVMと同様の役割を持つが、VSモード時にのみ有効であり、不正命令例外の代わりに仮想命令例外を生成する。VTSR=1の場合、VSモードにおいてSRET命令を実行しようとすると仮想命令例外が発生する。VTW=1の時(かつmstatus.TW=0の時)、VSモードにおいてWFI命令を実行し、かつ実装依存の特定のタイムリミット内に命令が完了しなかった場合に仮想命令例外が発生する。VTVM=1の場合、VSモードにおいてSFENCE.VMA命令を実行するか、satpレジスタにアクセスしようとすると仮想命令例外が発生する。

VGEIN(Virtual Guest External Interrupt Number)フィールドは、VSレベルの外部割込みにおいてゲストの外部割込みソースを選択する。VGEIENはWLRLのフィールドで、ゼロからゲストを外部割込み番号(この値をGEILENとする)までのどれかの値を設定する必要がある。VGEIN=0の場合、VSレベルの外部ら割り込みには、どのゲスト外部割込みソースも選択されていない。GEILENが0の場合、VGEINはゼロに固定されている。ゲストの外部割込みについては5.2.4節で説明されており、VGEINのより詳細については5.2.3節で説明されている。

hstatus.HUフィールド

HUフィールド(Hypervisor User mode)は仮想マシンのロード・ストア命令を制御する。HLV,HLVX, HSVフィールドはUモードにおいて使用される。HU=1の場合、これらの命令がUモードではHSモードと同様に実行することができる。HU=0の場合、Uモードでこれらの命令を実行しようとすると不正命令例外が発生する。

HUビットを使用すると、ハイパーバイザーの一部をUモードで実行して、仮想マシンのメモリへのアクセスを維持しながら、ソフトウェアのバグに対する保護を強化できる。

SPVビット(Supervisor Previous Virtualization

Mode)HSモードでトラップが発生した場合に実装によって書き込まれる。sttatusのSPPビットがトラップ時の特権モードの値を書き込むように、hstatusのSPVビットはトラップ時の仮想モードVの値を書き込む。V=0にSRETが実行されると、SPVにはVが設定される。

hstatus.SPVPフィールド

V=1時にトラップが発生しHSモードに遷移すると、sstatus.SPPと同様にトラップ時の特権モードがSPVP(Supervisor

Previous Virtual

Privilege)ビットに設定される。しかしトラップ前にV=0の場合には、SPVPはトラップ発生時には変更されない。SPVPは仮想マシンによって実行されるロードストア命令、HLV,

HLVX, HSVによる明示的なメモリアクセスの有効な特権を管理している。

SPVPがない場合、HLV、HLVX、およびHSVの命令が代わりに

sstatus.SPPを参照してメモリアクセスの有効な特権を探した場合、HU = 1の場合でも、UモードはVSレベルで仮想マシンメモリにアクセスできなかった。 SRETを使用してUモードに入ると、常にSPP = 0のままになる。 SPPとは異なり、フィールドSPVPは、HSモードとUモードの間を行ったり来たりする遷移の影響を受けない。

GVA(Guest Virtual

Address)フィールドはトラップが発生しHSモードに入った場合に実装により書き込まれる。仮想アドレスをstvalに書き込むようなトラップ(アクセス例外、ページフォルト、ゲストページフォルト)が発生した場合、GVAは1が設定される。HSモードに入るそれ以外のトラップでは、GVAは0に設定される。

メモリアクセス例外の場合、HLV, HLVX, またはHSV命令の明示的なメモリアクセスによって例外が発生する場合を除いて、GVAはSPVフィールドと冗長になる(これらの2ビットは同じ値が設定される)。これ以外の場合には、SPV = 0かつGVA = 1となる。

VSBEビットはWARLフィールドであり、VSモードによって実行されるメモリアクセスのエンディアンを制御する。VSBE=0の場合、VSモードでの明示的なロードストアメモリアクセスはリトルエンディアンであり、VSBE=1の場合にはビッグエンディアンとなる。VSBEはVSレベルのページテーブルのようなメモリ管理データ構造の暗黙的なメモリアクセスについても制御を行う。VSBEをRead-Onlyに実装することで、常にHSモードと同じエンディアンを求めることも可能である。

5.2.2 ハイパーバイザーTrap移譲レジスタ (hedeleg / hideleg)¶

hedelegとhidelegはHSXLENビットの読み書き可能なレジスタで、図5.3と図5.4にそれぞれレジスタのフォーマットを示す。デフォルトでは、すべての特権レベルのすべてのトラップはMモードで処理されるが、通常はmedelegとmidelegCSRレジスタを使用していくつかのトラップをHSモードに移譲する。hedelegとhidelegCSRはこれらのトラップをさらにVSモードゲストに移譲することができる;

これらのレジスタのレイアウトはmedelegとmidelegのレイアウトと同一である。

図5.3:ハイパーバイザー例外移譲レジスタ(hedeleg)¶

図5.4:ハイパーバイザー割り込み移譲レジスタ(hideleg)¶

ビット |

属性 |

該当する例外 |

|---|---|---|

0 |

(本文を参照のこと) |

命令アドレスミスアライン |

1 |

書き込み可能 |

命令アクセスフォルト |

2 |

書き込み可能 |

不正命令例外 |

3 |

書き込み可能 |

ブレークポイント |

4 |

書き込み可能 |

ロードアドレスミスアライン |

5 |

書き込み可能 |

ロードアクセスフォルト |

6 |

書き込み可能 |

ストア/AMOアドレスミスアライン |

7 |

書き込み可能 |

ストア/AMOアクセスフォルト |

8 |

書き込み可能 |

Environment Call from Uモード or VUモード |

9 |

読み込み専用 0 |

Environment Call from HSモード |

11 |

読み込み専用 0 |

Environment Call from Mモード |

12 |

書き込み可能 |

命令ページフォルト |

13 |

書き込み可能 |

ロードページフォルト |

15 |

書き込み可能 |

ストア/AMOページフォルト |

20 |

読み込み専用 0 |

命令ゲストページフォルト |

21 |

読み込み専用 0 |

ロードゲストページフォルト |

22 |

読み込み専用 0 |

仮想命令 |

23 |

読み込み専用 0 |

ストア/AMOゲストページフォルト |

表5.2: hedelegの書き込み可能ビットと0に固定されているビット

medelegを使用してHSモードに移譲される同期トラップは、V=1の場合にhedelegビットがセットされている場合にさらにVSモードまで移譲される。hedelegは書き込み可能なビットと、0に固定されているビットがある。hedelegの多くのビットは書き込み可能もしくはゼロ固定であり、表5.2それらをまとめている。命令アドレスミスアラインに相当するビット0についてはIALIGN=32の場合にのみ書き込み可能としなければならない。

hedelegの特定のビットが書き込み可能であることを要求することにより、実装のバリエーションを処理するためのハイパーバイザーの負担が軽減される。

midelegを使用してHSモードに移譲される例外は、hidelegのビットが設定されている場合にさらにVSモードまで移譲される。hidelegの15:0ビットのうち10ビット、6ビット、2ビットのみ書き込み可能である(これらは標準VSレベル割り込みに相当する)、それ以外のビットはゼロに固定されている。

仮想スーパバイザ―外部例外(要因コード10)がVSモードに渡されると、例外は自動的にVSモードのためにスーパーバイザー外部割込み(要因コード9)に移譲される。例外要因コードは同時にvscauseにも書き込まれる。同様に、仮想スーパーバイザータイマー割り込み(要因コード6)はVSモードにてスーパーバイザータイマー割り込み(要因コード5)に変換され、仮想スーパーバイザーソフトウェア割り込み(要因コード2)はVSモードにてスーパーバイザーソフトウェア割り込み(要因コード1)に変換される。同様の変換はプラットフォームかカスタム割り込み要因(要因コード16以上)にも適用される可能性がある。

5.2.3 ハイパーバイザー割り込みレジスタ (hvip, hip, hie)¶

hvipはHSXELNビットの読み書き可能なレジスタであり、ハイパーバイザーが該当する仮想割り込みをVSモードのために書き込むことができるかどうかを示す。hidelegにおける書き込み可能なビットは、hvipにおいても同様に書き込み可能であり、そうでないビットは同様に0に固定されている。

図5.5:ハイパーバイザー仮想割り込みペンディングレジスタ(hvip)¶

hvipの標準的なビット位置(ビット15:0)のフォーマットを図5.6に示す。hvipのVSEIP=1に設定することにより、VSレベルの外部割込みがアサートされる;

VSTIPを設定することにより、VSレベルのタイマー割り込みがアサートされる;

VSSIP=1に設定することによりVSレベルのソフトウェア割り込みがアサートされる。

図5.6:hvipの標準的なビット位置¶

hipおよびhieレジスタはHSXELNビットの読み書き可能なレジスタであり、HSレベルのsipおよびsieレジスタをそれぞれ補完するものである。hipレジスタはVSレベルおよびハイパーバイザー固有の割り込みがペンディングしていることを示すレジスタであり、一方でhieは割り込みが許可されているかどうかを示している。sipとsieは、割り込みiはhipとhieの同じビットiが設定され、かつスーパーバイザレベルの割り込みがグローバルに有効化されている場合にはHSモードでトラップされる。

図5.7:ハイパーバイザー割り込みペンディングレジスタ¶

図5.8:ハイパーバイザー割り込み許可レジスタ(hie)¶

sieにおける書き込み可能なビットは、hipおよびhieにおいてゼロに固定されている。したがって、sieおよびhieのゼロでないビットは常に排他的であり、sipおよびhipも同様である。

hipおよびhieの有効なビットはHSレベルのsipおよびsieには配置することができない。なぜならば、そのようにするとソフトウェアがハイパーバイザー拡張が実装されていないハードウェアにおいてハイパーバイザーをソフトウェアがエミュレートすることができないからである。

sieのiビットがゼロに固定されている場合、hipの同じビットは書き込み可能であるか、読み込み専用である。もしhipのビットiが書き込み可能である場合、当該ビットに0を書き込むことにより、そのペンディングビットをクリアすることができる。もし割り込みiがhipのビットを設定することができるものの、hipの当該ビットが読み込み専用である場合、hvipの当該ビットをクリアするか、Execution

Environmentコールを含む割り込みペンディングをクリアするためのいくつかのメカニズムを提供することが必要である。

hipにおいてペンディングすることのできるビットは、hieにおいても同じビットは書き込むことができる。hieの書き込みできないビットはゼロに固定されている。

図5.9:hipの標準的なビット配置(ビット15:0)¶

図5.10:hieの標準的なビット配置(ビット15:0)¶

hip.SGEIPおよびhip.SGEIEはスーパーバイザーレベル(HSレベル)のゲスト外部割込み向けの割り込みペンディングビットおよび割り込み許可ビットである。SGEIPはhipにおいては読み込み専用で、hgeipCSRおよびhgeieCSRの任意のビットがゼロでない場合の論理積が1である場合にのみ1が設定される。

hip.SSEIPおよびhie.VSEIEはVSレベルでの外部割込み向けの割り込みペンディングビットおよび割り込み許可ビットである。VSEIPはhipにおいて読み込み専用であり、以下の割り込み要因の論理ORである:

hvip.VSEIPビットhstatus.VGEINにより選択されたhgeipビット; およびVSレベルで指定される任意のプラッタフォーム独自の外部割込み信号

hip.VSTIPおよびhie.VSTIEビットはVSレベルのタイマー割り込みの割り込みペンディングビットおよび割り込み許可ビットである。VSTIPはhipにおいて読み込み専用であり、hvipの論理ORである。VSTIPはhipにおいて読み込み専用であり、hvipの論理ORである。VSTIPおよび他の任意のプラットフォーム固有のタイマー割り込み信号はVSレベルに送信される。

hip.VSSIPおよびhie.VSSIEビットはVSレベルのソフトウェア割込みの割り込みペンディングビットおよび割り込み許可ビットである。hipのVSSIPビットはhvipの当該ビットの(書き込み可能な)エイリアスである。

HSモードにおける複数同時の割り込みが発生した場合、以下の降順の優先度によって処理される:SEI, SSI, STI, SGEI, VSEI, VSSI, VSTI。

5.2.4 ハイパーバイザーゲスト外部割込みレジスタ (hgeipおよびhgeie)¶

hgeipレジスタはHSXLENビットの読み込み専用レジスタであり、図5.11に示すビットフォーマットで構成されている。このレジスタは当該HARTにおけるペンディングしていているゲスト外部割込みを示している。hgeieレジスタはHSXLENビットの読み書き可能なレジスタであり、図5.12に示すビットフォーマットで構成されている。このレジスタは当該HARTにおけるゲスト外部割込みの割り込み許可ビットである。ゲスト外部割込みの要因番号iが、hgiepとhgeieのビットiに相当する。

図5.11:ハイパーバイザーゲスト外部割り込みペンディングレジスタ(hgeip)¶

図5.12:ハイパーバイザーゲスト外部割込み許可レジスタ¶

VSレベルでは、ゲスト外部割込みは個々の仮想マシンに対する割込みとして表現される。RISC-Vプラットフォームが、ハイパーバイザーの介入を最小限にしてゲストOSの直接制御下に物理デバイスを配置することをサポートしている場合(仮想マシンと物理デバイス間のパススルーや直接割り当てと言われている)、そのような状況では、デバイスからの割り込みは特定の仮想マシンを対象としている。hgeipの各ビットは、割り込みコントローラが収集して報告した、1つの仮想マシンに向けられた全ての保留中の割り込みをまとめたものである。複数のデバイスからの特定の保留中の割り込みを区別するためには、ソフトウェアは割り込みコントローラに問い合わせなければならない。

ゲスト外部割込みをサポートするためには、割り込みコントローラ型の割り込みとは個別に仮想マシンに向けられた割り込みを収集できなければならない。

hgeipおよびhgeieに実装された割り込みの数は指定されておらず、おそらくゼロである。この値をGEILENと呼び、0ビット目を含む下位のビットから先に実装される。従ってもしGEILENがゼロでない場合、hgeieのGEILEN:1ビットは書き込み可能であり、hgeipおよびhgeieの他のビットはゼロに固定されている。

1つの物理HARTで受信して処理されるゲスト外部割込みのセットは、他のHARTで受信したものとは異なる場合がある。1つの物理HARTでのゲスト外部割込み番号

iは、通常、他のHARTでのゲスト外部割込み番号iと同じではないことが予想される。1つの物理HARTに対して、ゲスト外部割込みを直接受信できる仮想HARTの最大数はGEILENによって制限されている。この数の最大値は、どのような実装でも、物理HARTごとに、RV32では31個、RV64では63個である。ハイパーバイザーは、GEILENによって制限されることなく、仮想HARTの数に関係なく、常に自由にデバイスをエミュレートすることができます。割り込みの直接パススルー(直接割り当て)のみがGEILENの制限の対象となる。1つの仮想HARTが受け取ることができる個別の割り込みの数は、割り込みコントローラによって決定される。

hgeieレジスタはスーパーバイザーレベル(HSレベル)で発生するゲスト外部割込みの一部を選択する。hgeieの割り込み許可ビットは、hstatus.VGEINにより選択されるhgeipのVSレベルでの外部割込み信号に影響を与えない。

5.2.5 ハイパーバイザーカウンタ許可レジスタ (hcounteren)¶

カウンタ許可レジスタhcounterenはゲスト仮想マシン向けのハードウェアパフォーマンスモニタリングカウンタの利用可能状態を制御するための32ビットレジスタである。

図5.13:ハイパーバイザーカウンタ許可レジスタ(hcounteren)¶

hcounterenレジスタのCY、TM、IR、HPMnビットがクリアされている場合、V=1時にcycle,

time, instret,

hpmcounternレジスタを読もうとすると、mcounterenの当該ビットが1であったとしても仮想命令例外が発生する。これらのビットがセットされている場合、V=1の時は、他に任意の理由でアクセスが禁止されていたとしても、当該レジスタへのアクセスは許可される。VUモードでは、hcounterenとscounterenのビットが設定されていたとしても、これらのカウンタの値は読み取ることができない。

hcounterenは常に実装されていなければならない。しかし、任意のビットの値はゼロに固定することができ、これはV=1のときに当該カウンタの値を読もうとすると例外が発生することを意味する。したがって、これらのビットはWARLフィールドであると言える。

ハイパーバイザータイムデルタレジスタ (htimedelta, htimedeltah)¶

htimedeltaCSRはtimeレジスタの値とVSモードおよびVUモードでの返される値の差分を保持している。つまり、timeCSRをVSモードおよびVUモードで読むと、htimedeltaとtimeの実際の値を加算した結果が返される。

htimedeltaとtimeの加算におけるオーバーフローは無視されるため、htimedeltaの値が大きくなると、タイムオフセットの負の値して取り扱われる。

図5.14:ハイパーバイザータイムデルタレジスタ, HSXLEN=64¶

HSXLEN=32では、htimedeltaはデルタ値の下位32ビットを保持している。htimedeltahはデルタ値の上位32ビットを保持している。

図5.15:HSXLEN=64時のハイパーバイザータイムデルタレジスタ¶

5.2.7 ハイパーバイザートラップ値レジスタ(htval)¶

htvalレジスタはHSXLENビットの読み書き可能なレジスタで、図5.16に示すフォーマットで構成されている。トラップによりHSモードに入ると、stvalと一緒にhtvalに例外要因固有の情報が書き込まれ、ソフトウェアがトラップを処理するために使用される。

図5.16:ハイパーバイザートラップ値レジスタ(htval)¶

ゲストページフォルト例外によりHSモードに移行した場合、htvalにはゼロもしくは例外の発生したゲスト物理アドレスを2ビット右にシフトした値が書き込まれる。他の例外では、htvalの値はゼロに設定されるが、将来の仕様アップデートや他の拡張によってhtvalの挙動が異なる可能性がある。

ゲストページフォルト例外は第1ステージ(VSステージ)のアドレス変換による暗黙的なメモリアクセスにより発生する可能性があるが、この場合にはhtvalに書き込まれるゲスト物理アドレスは、例外の発生した暗黙的なメモリアクセスのアドレスとなる。例えば、VSレベルのページテーブルエントリのメモリ読み込みに失敗した場合などである。(VSステージでの変換が完了しなかった場合、オリジナルの仮想アドレスに相当するゲスト物理アドレスは未知である。)このような状態における曖昧さを削減するための更なる情報としてhtinstCSRが使用される。

そうでない場合、ミスアラインロード・ミスアラインストアによりゲストページフォルトが発生する場合には、htvalにはstvalに格納されている仮想アドレスに対応する変換に失敗した物理アドレスが返される。可変長の命令を持つシステムでの命令ゲストページのフォルトの場合、ゼロではないhtvalは、stvalの仮想アドレスで示される命令のフォルト部分に対応する。

htvalに書き込まれたゲスト物理アドレスは、現在のXLENよりも広いアドレスに対応するために2ビット右にシフトされる。RV32 では、ハイパーバイザ拡張により、34ビットのゲスト物理アドレスが許可され、htvalはそのアドレスの33:2ビットを報告する。このゲスト物理アドレスの2ビットシフトエンコーディングは、PMPアドレスレジスタ (Section 3.6) とページテーブルエントリ (Section 4.3, 4.4, 4.5) の物理アドレスのエンコーディングと一致している。

例外の発生したゲストの物理アドレスの最下位2ビットが必要な場合、これらのビットは通常、stvalの故障している仮想アドレスの最下位2ビットと同じである。VSステージのアドレス変換のための暗黙のメモリアクセスによる例外の場合、最下位2ビットは代わりにゼロになる。これらのケースは、レジスタ

htinstで提供される値を用いて識別することができる。

htvalはWARLレジスタであり、ゼロを保持していなければならず、ゲスト物理アドレスの2ビットシフトされたサブセットのみを保持することができる。

(プラットフォーム標準などの)他の理由がない限り、ソフトウェアにより``htval``を書き込んだ場合にはその値が

htvalからリードバックできなければならない。

5.2.8 ハイパーバイザ―トラップ命令レジスタ (htinst)¶

htinstレジスタはHSXLENビットの読み書き可能なレジスタであり、図5.17に示されるビットフォーマットで構成されている。トラップが発生しHSモードに移行した場合、htinstはゼロでない場合例外の発生した命令の情報を保持しており、ソフトウェアによりトラップを処理するのを助ける役割を持っている。htinstに書き込まれる値に抜いてはSection

5.6.3で説明している。

図5.17:ハイパーバイザートラップ命令レジスタ¶

htinstはWARLレジスタであり、実装がトラップ発生時に自動的に書き込んだ値を保持しておかなければならない。

5.2.9 ハイパーバイザーゲストアドレス変換および保護レジスタ (hgatp)¶

htatapレジスタはHSXLENビットの読み書き可能なレジスタであり、HSXLEN=32の場合のビットフォーマットを図5.18に、HSXLEN=64の場合のビットフォーマットを図5.19に示す。このレジスタはゲスト仮想アドレス変換の2番目のステージであるGステージアドレス変換の制御及び保護を行う(5.5節を参照のこと)。satpCSRレジスタと同様に、このレジスタはゲスト物理ルートページテーブルの物理ページ番号(PPN)、仮想マシン毎のアドレス変換を区別するための仮想マシン識別番号(VMID)、下種て物理アドレスの変換方法を選択するためのMODEフィールドから構成されている。mstatus.TVM=1の場合、HSモードでのhgatpレジスタを読み書きしようとすると命令例外が発生する。

表5.3はRV32とRV64におけるMODEフィールドのエンコーディングを示している。MODE=Bareでは、ゲスト物理アドレスはスーパーバイザー物理アドレスと同一であり、3.6節で示すようにゲスト仮想マシンと物理メモリ保護については追加的な保護は存在しない。この場合には、hgatpのほかのフィールドはゼロに設定していなければならない。

RV32では、MODEの有効な設定はSv32x4のみである。このモードでは通常のSv32ページ仮想メモリ方式を修正したもので、34ビットゲスト物理アドレスをサポートするために拡張したものである。RV64ではSv39x4およびSv48x4が定義されており、これはSv39およびSv49ページ仮想メモリ方式を修正したものである。これらのすべてのページ仮想メモリ方式については5.5.1節で説明している。RV64でさらに追加されている方式としてSv57x4が定義されており、これは仕様書の今後のバージョンで定義される予定である。

RV64におけるMODEフィールドの他の値については将来のために予約されており、hgatpの他のフィールドの異なる解釈のために使用される予定である。

表5.3:hgatp MODEフィールドのエンコーディング¶

RV64の実装では、すべてのRV64 MODE設定をサポートする必要はない。

hgatpにおけるサポートされないMODEの書き込みは、satpのように無視されない。その代わり、hgatpのフィールドはWARLフィールドであり、そのような書き込みが発生した場合は識別される。

メモ:WARLとは Write Any Value, Read Legal Value。

一部の読み書きCSRフィールドは、一部のビットエンコーディングに対してのみ定義されていますが、読み出しの際には必ず適法な値を返すことを保証しながら、任意の値を書き込むことができます。CSRの書き込みに他の副作用がないと仮定して、サポートされている値の範囲を決定するには、希望の設定を書き込んでみて、その値が保持されているかどうかを確認するために読み出すことができます。これらの値は、レジスタの説明ではWARLと表示されています。

WARLフィールドへのサポートされていない値の書き込みで例外が発生することはありません。実装では、最後の書き込みが不正な値であった場合、WARLフィールドの読み出しで任意の正規の値を返すことができますが、返される正規の値は、不正に書き込まれた値とハートのアーキテクチャ状態に決定論的に依存します。

5.5.1節で説明しているように、ページ仮想メモリ方式(Sv32x4, Sv39x4,

Sv48x4)では、ルートページテーブルは16kiBであり16KiB協会にアラインしていなければならない。これらのモードへは、hgatp内の物理ページ番号(PPN)フィールドの最下位2ビットは常にゼロが読みだされる。定義されているページ仮想メモリ方式のBareのどちらか、あるいは両方のみをサポートしている実装では、PPN[1:0]はゼロに固定していなければならない。

VIMDのビット数は定義されていないか、あるいはゼロである。VMIDの実装されているビット数のことをVMIDLENと定義されるが、これはVMIDフィールドのすべてのビットに1を書き込み、hgatpの当該ビットをリードバックすることで保持されている1の数を調査することで識別できる。VMIDは下位のビットから先に実装される:つまり、VMIDLEN>0であれば、VMID[VMIDLEN-1:0]が書き込み可能である。VMIDLENの最大値(これをVMIDMAXと呼ぶ)はSv32x4では7であり、Sv39x4およびSv48x4では14である。

hgatpページテーブルのアップデートと後続のGステージアドレス変換の順番を制約しているわけではない。新しい仮想マシンのゲスト物理ページテーブルが変更されると、hgatpへの書き込みを行う前にHFENCE.GVMA命令を実行する必要がある可能性がある(5.3.2節を参照のこと)。

5.2.10 仮想スーパーバイザーステータスレジスタ (vsstatus)¶

vsstatusレジスタはVSXLENビットの読み書き可能なレジスタであり、VSモードでのスーパーバイザーステータスsstatusである。図5.20にVSXLEN=32でのビットフォーマット、図5.21にVSXLEN=64でのビットフォーマットを示す。V=1の場合に、vsstatusはsstatusの代替の役目を担い、従ってsstatusを読み書きする命令はすべてvsstatusに置き換えられる。

図5.20:RV32向け仮想スーパーバイザーステータスレジスタ(vsstatus)¶

図5.21:RV64向け仮想スーパーバイザーステータスレジスタ(vsstatus)¶

UXLフィールドはVUモードでのXLEN値を制御しており、VSモードでのXLEN値(VSXLEN)とは異なる可能性がある。VSXLEN=32の場合、UXLフィールドは存在せず、VUモードでのXLEN=32である。VSXLEN=64の場合はUXLフィールドはWARLフィールドであり、16ページの表3.1におけるmisaレジスタにおけるMXLのエンコーディングと同様である。特に、実装によってはUXLを読み込み専用フィールドとし、hstatutsのVSXLフィールドをコピーすることで強制的にVUモードにおいてXLEN=VSXLENとすることもできる。

VSXLENが32よりも大きな値に変更されると、UXLは単一の値に制限されなくなり、新しいVSXLENよりも小さな最も大きなサポート可能な値に変更される。

V=1の場合、vsstatus.FSおよびHSレベルでのsstatus.FSが有効である。どちらかのフィールドが0(Off)である場合、浮動小数点命令を実行しようとすると命令違反例外が発生する。V=1の時、浮動小数点のステートを変更すると、どちらのフィールドも3(Dirty)に変更される。

ハイパーバイザーが拡張コンテキストステータスの恩恵を受けるためには、VSモードで動作するゲストOSから独立して維持されているHSレベルの

sstatusにそれ自身のコピーを持たなければならない。拡張コンテキスト状態のバージョンは明らかにVSモード用のvsstatusに存在しなければならないが、VSレベルのソフトウェアがvsstatus.FSを任意に変更できることを考えると、ハイパーバイザーはこのバージョンが正しく維持されているかどうかに頼ることはできない。V=1の間、HSレベルのsstatus.FSが独立してアクティブでなく、ハードウェアによってvsstatus.FSと並行して維持されていない場合、ハイパーバイザーは、仮想マシン間でコンテキストを切り替える際に、常に保守的にすべての拡張ポイントの状態をスワップすることを余儀なくされることになる。

読み込み専用のSDおよびXSフィールドは拡張コンテキストの状態を示しており、VSモードでのみ参照することができる。例えばHSレベルのsstatus.FSはvsstatus.SDに影響を与えない。

実装は、UBEをhstatus.VSBEの読み込み専用コピーとすることができる。

V=0の場合、vsstatusはマシンの動作に直接影響を与えないが、仮想マシンロードストア(HLV/HLVX/HSV)もしくはmstatusレジスタのMPRV機能は例外であり、V=1の時のようにロードストアを実行する際に使用される。

5.2.11 仮想スーパーバイザー割り込みレジスタ (vsip, vsie)¶

vsipとvsieはVSXLENビットの読み書き可能なレジスタで、sipとsieレジスタのVSモード版である。それぞれのビットフォーマットを図5.22および図5.23に示す。V=1の時、vsipとvsieはsipとsieの代替であり、sipおよびsieに対して読み書きを行う命令は、これらの命令に対する読み書きに置き換わる。しかし、HSレベルに挿入される割込みは引き続きHSレベルのsipレジスタが使用され、V=1の場合でもvsipは使用されない。

図5.22:仮想スーパーバイザー割り込みペンデングレジスタ(vsip)¶

図5.23:仮想スーパーバイザー割り込み許可レジスタ(vsie)¶

vsipとvsieの標準的なビット配置(ビット15:0)を図5.24と図5.25に示す。

図5.24:vsipの標準的なビット配置¶

図5.24:vsieの標準的なビット配置¶

hidelegのビット10が0の場合、vsip.SEIPとvsie.SEIEはゼロに固定されている。そうでなければ、vsip.SEIPとvsie.SEIEはhip.VSEIPとhie.VSEIEのエイリアスである。

hidelegのビット6が0の場合、vsip.STIPとvsie.STIEはゼロに固定されている。そうでなければ、vsip.STIPとvsie.STIEはhip.VSTIPとhie.VSTIEのエイリアスである。

hidelegのビット2が0の場合、vsip.SSIPとvsie.SSIEはゼロに固定されている。そうでなければ、vsip.SSIPとvsie.SSIEはhip.VSSIPとhie.VSSIEのエイリアスである。

メモ:

Spikeにおけるvsipとvsieの挙動:mieとmipを参照しているなあ。hieとhipもmieとmipを参照している。

void processor_t::set_csr(int which, reg_t val)

{

/* ... */

case CSR_VSIE: {

reg_t mask = state.hideleg & MIP_VS_MASK;

state.mie = (state.mie & ~mask) | ((val << 1) & mask);

break;

}

/* ... */

case CSR_VSIP: {

reg_t mask = state.hideleg & MIP_VSSIP;

state.mip = (state.mip & ~mask) | ((val << 1) & mask);

break;

}

case CSR_HIE: {

reg_t mask = MIP_HS_MASK;

state.mie = (state.mie & ~mask) | (val & mask);

break;

}

case CSR_HIP: {

reg_t mask = MIP_VSSIP;

state.mip = (state.mip & ~mask) | (val & mask);

break;

}

}

reg_t processor_t::get_csr(int which, insn_t insn, bool write, bool peek)

{

case CSR_VSIE: ret((state.mie & state.hideleg & MIP_VS_MASK) >> 1);

/* ... */

case CSR_VSIP: ret((state.mip & state.hideleg & MIP_VS_MASK) >> 1);

case CSR_HIE: ret(state.mie & MIP_HS_MASK);

case CSR_HIP: ret(state.mip & MIP_HS_MASK);

}

5.2.12 仮想スーパーバイザートラップベクタベースアドレスレジスタ (vstvec)¶

vstvecレジスタはVSXLENビットの読み書き可能なレジスタであり、スーパーバイザーレジスタstvecのVSモード版である。ビットフォーマットを図5.26に示す。V=1の場合、vstvecは通常のstvecの代替となり、通常のstvecへの読み書きを行う命令はvstvecへの読み書きへと置き換えられる。V=0の場合はvstvecはマシンの動作には一切影響を与えない。

図5.26:仮想スーパーバイザートラップベクタベースアドレスレジスタ¶

メモ:Spikeにおけるvstvecの動作

void processor_t::set_csr(int which, reg_t val)

{

...

case CSR_STVEC: // STVECへの参照時:V=1の場合はvstvecに書き込まれる

if (state.v)

state.vstvec = val & ~(reg_t)2;

else

state.stvec = val & ~(reg_t)2;

break;

...

case CSR_VSTVEC: state.vstvec = val & ~(reg_t)2; break;

...

}

void processor_t::get_csr()

{

...

case CSR_STVEC: { // STVECの読み出し時、V=1の場合はvstvecが読みだされる。

if (state.v) {

ret(state.vstvec);

} else {

ret(state.stvec);

}

}

case CSR_VSTVEC: ret(state.vstvec);

}

5.2.13 仮想スーパーバイザースクラッチレジスタ (vsscratch)¶

vsscratchレジスタはVSXLENビットの読み書き可能なレジスタであり、スーパーバイザーモードのsscrtachのVSモードにおける大体である。ビットフォーマットを図5.27に示す。V=1の時、vsscratchはsscratchの代替であり、従って通常のsscratchへのアクセス命令はvsscratchに置き換えられる。vsscratchの値はマシンの動作に直接影響を与えない。

図5.27:仮想スーパーバイザースクラッチレジスタ(vsscratch)¶

5.2.14 仮想スーパーバイザー例外プログラムカウンタ (vsepc)¶

vsepcレジスタはVSXLENビットの読み書き可能なレジスタであり、スーパーバイザーモードのsepcレジスタのVSモードでの代替である。ビットフォーマットを図5.28に示す。V=1の時、vsepcは通常のsepcの代替であり、従って通常のsepcレジスタへの読み書き命令はvsepcへのアクセスへ置き換えられる。V=0の時、このレジスタはマシンの動作に影響を与えない。

5.2.15 仮想スーパーバイザー要因レジスタ (vscause)¶

vscauseレジスタはVSXLENビットの読み書き可能なレジスタであり、スーパーバイザーモードのscauseレジスタのVSモードでの代替である。ビットフォーマットを図5.29に示す。V=1の場合、vscauseは通常のscauseのように動作するため、scauseへのアクセス命令はvscauseへのアクセスへ置き換えられる。V=0の場合、vscauseはマシンの動作に影響を与えない。

vscauseはWLRLレジスタのため、scauseが保持することのできる値と同様の値を保持できなければならない。

図5.29:仮想スーパーバイザー要因レジスタ(vscause)¶

5.2.16 仮想スーパーバイザートラップ値レジスタ (vstval)¶

vstvalレジスタはVSXLENビットの読み書き可能なレジスタであり、スーパーバイザーモードのstvalレジスタのVSモードでの代替である。ビットフォーマットを図5.30に示す。V=1の時、vstvalは通常のstvalのように動作するため、stvalへのアクセス命令はvstvalへのアクセスへ置き換えられる。V=0の場合、vstvalはマシンの動作に影響を与えない。

vstvalはWARLレジスタのため、stvalが保持することのできる値と同様の値を保持できなければならない。

図5.30:仮想スーパーバイザートラップ値レジスタ(vstval)¶

5.2.17 仮想スーパーバイザーアドレス変換および保護レジスタ (vsatp)¶

vsatpレジスタはVSXLENビットの読み書き可能なレジスタであり、スーパーバイザーモードのsatpレジスタのVSモードでの代替である。図5.31にVSXLEN=32のビットフォーマットを、図5.32にVSXLEN=64のビットフォーマットを示す。V=1の時、vsatpレジスタはsatpレジスタの代替であり、従って通常のsatpレジスタへの読み書き命令はvsatpへの読み書きに置き換えられる。vsatpレジスタはゲスト仮想アドレスの2ステージ変換における最初のステージであるVSステージのアドレス変換を制御する(5.5節を参照のこと)。

図5.31:RV32時の仮想スーパーバイザーアドレス変換及び保護レジスタ(vsatp)¶

V=0の場合、vsatpへのサポートされないMODE値を書き込むと、satpレジスタのように無視されるわけではない。その代わりに、vsatpへのこのような書き込みはWARLとして取り扱われる。

V=0の場合、vsatpはマシンの動作に直接影響を与えない。ただし仮想マシンのロードストア命令(HLV,

HLVX,

HSV)の挙動およびmstatusレジスタにおけるMRPVの挙動は、V=1かどうかに関わらずロードストア命令のために使用される。

VTSR / VTW, VTVMビット :mstatusと同様だが、V=1の時に、RSET,WFI命令で使用される。SPV(Supervisor Previous Virtualization Mode)ビット : 例外が発生したときにの、仮想モードの情報を記録する。V=0時にSRET命令が実行されると、SPVにVが設定される。HSモード時に例外が発生すると、例外が発生する前にSP2VとSP2PにSPVとHSレベルのSPPの値が設定される(例外の前に、HSレベルのSPPはV=0時には

sstatus.SPPであり、V=1時にはbssatus.SPPである)。V=0のときにSRET命令が実行されると、逆の操作が行われる: つまり、SPVとsstatus.SPPが新しい仮想モードの例外モードに設定される:つまり、それぞれの値はSP2V, SP2Pに書き込まれる。STL(Supervisor Translation Level)はメモリアクセス失敗、ページ例外時のアドレス変換レベルを示している。HSモードで例外が発生した場合には必ず設定される。ゲスト物理アドレス変換中によるアクセス例外が発生した場合 : STLは1が設定される。

他の例外の場合には : STLは0が設定される。

SPRVビット

SPRV=0の場合 : メモリアクセス・プロテクションは通常通り行われる。

SPRV=1の場合 : ロード・ストアメモリアクセスは、現在の仮想モードがhstatus.SPVとして扱われ、現在の特権モードがHSレベルのSPPとして扱われる(V=0の場合は

sstatus.SPPが使用され、V=1の場合はbsstatus.SPPとなる)。

1540737909818¶

hedeleg, hidelegレジスタはHypervisor向けの移譲レジスタである。